# Projeto de Formatura – 2025

## PCS - Departamento de Engenharia de Computação e Sistemas Digitais

### Engenharia Elétrica – Ênfase Computação

Tema: **Sistema de medição para sensores ópticos aplicados a Sistemas Elétricos de Potência, com digitalização e comunicação avançada**

## INTRODUÇÃO

A calibração de transformadores de alta tensão é atualmente um processo complexo que exige o desligamento da rede. Visando superar esse desafio, este trabalho explora o uso de sensores ópticos como ferramentas portáteis para calibração *in situ*. O projeto desenvolve uma plataforma de hardware atualizada com protocolo PTP, permitindo a comparação precisa e em tempo real entre o sensor óptico e o equipamento convencional. A solução valida a metrologia óptica tanto para a manutenção do parque instalado quanto para futuras aplicações em subestações digitais.

## OBJETIVOS

Projetar e validar experimentalmente uma arquitetura de hardware atualizada para sensores ópticos, evoluindo os estudos de Nagao Jr. (2017) visando a futura aplicação em subestações digitais (IEC 61850). Foram feitos:

- Mapeamento e Análise:** Identificar limitações da arquitetura original e requisitos para Merging Units (timestamping e latência).

- Modernização do Hardware:** Propor novo esquemático substituindo componentes obsoletos por FPGA e Microcontroladores de alto desempenho.

- Sincronismo Temporal:** Desenvolver uma Prova de Conceito (PoC) do protocolo IEEE 1588 (PTP), validando a sincronização entre mestre e servo.

## DESENVOLVIMENTO

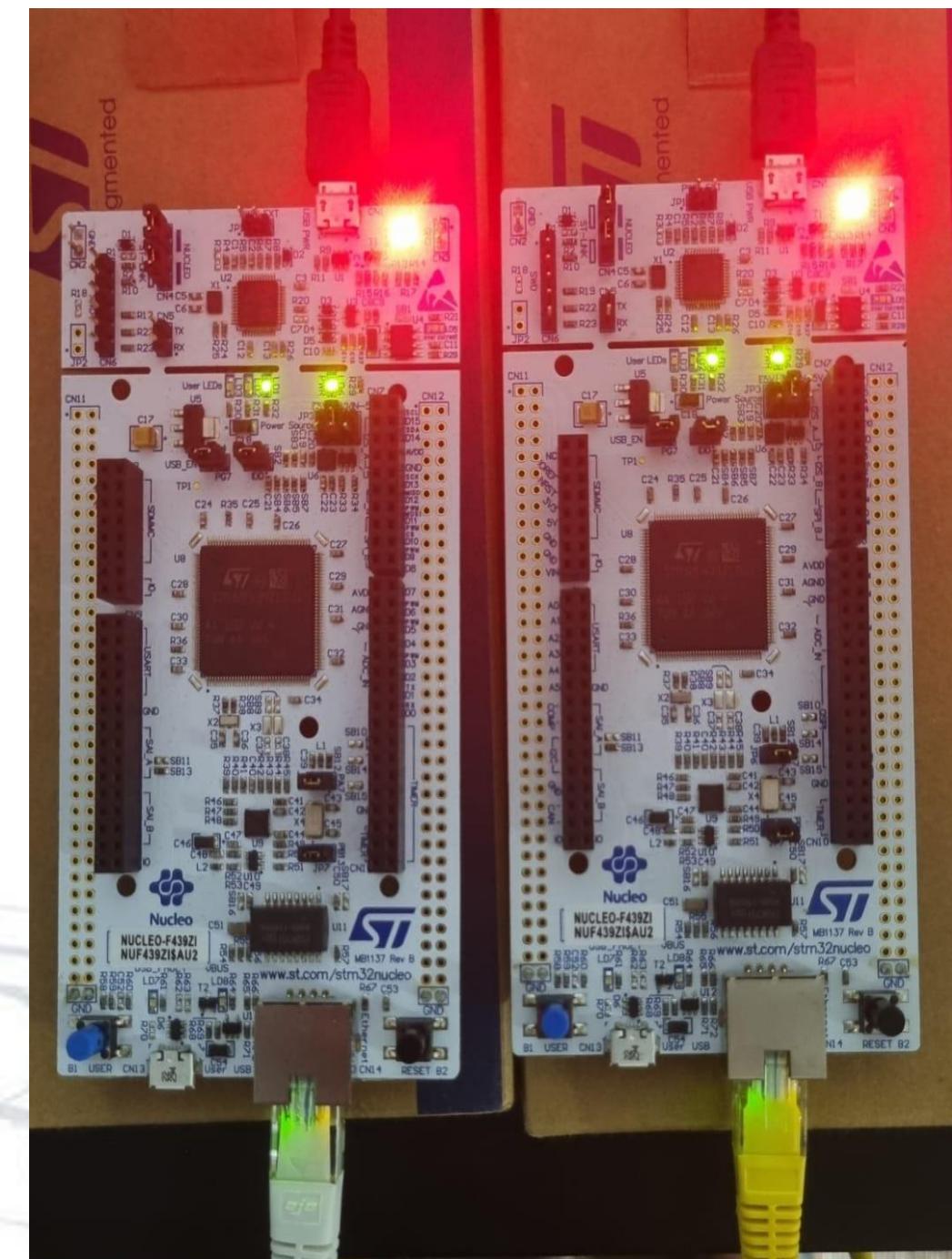

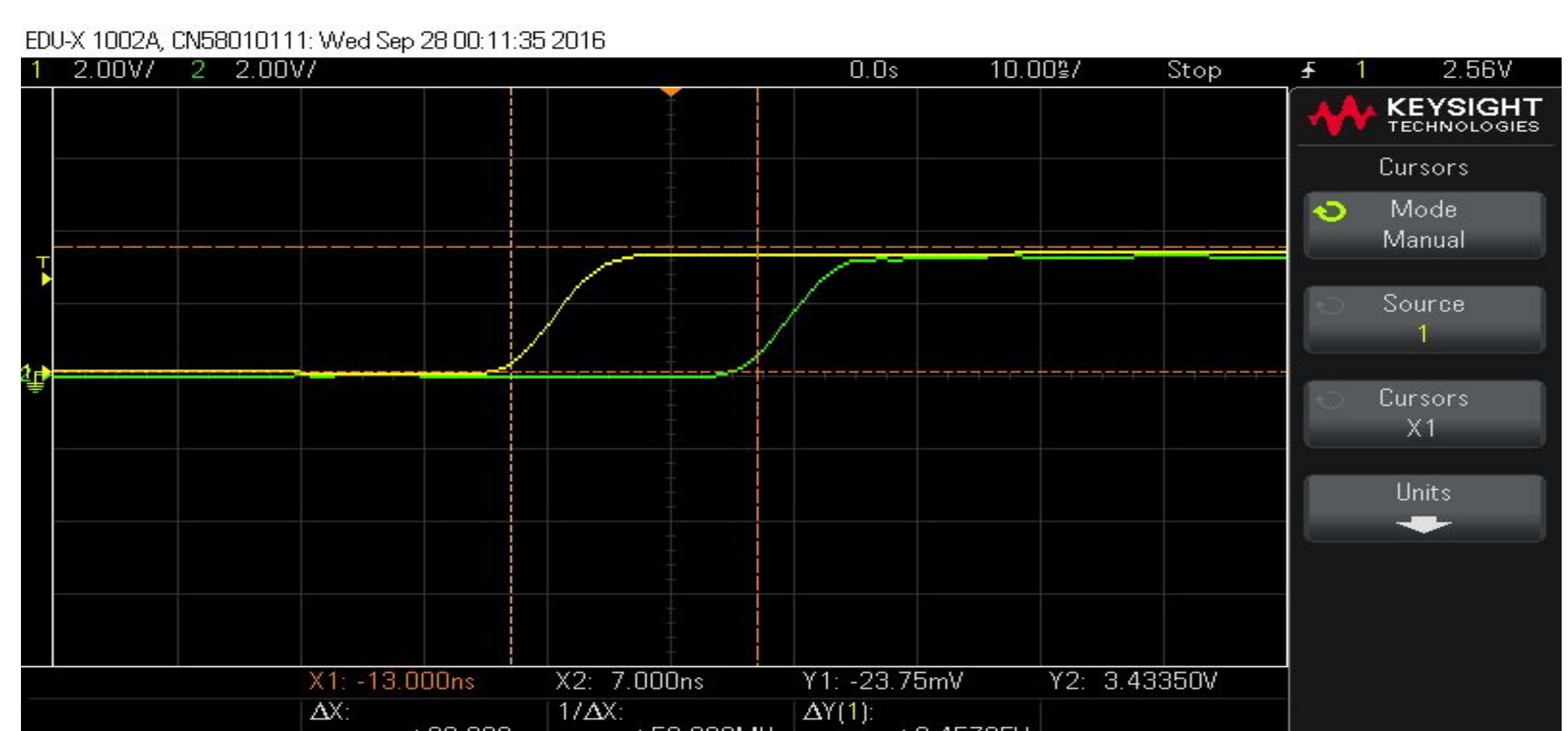

Para a implementação do sincronismo temporal, adotou-se o protocolo IEEE 1588 (PTP) utilizando microcontroladores STM32F429ZI e a biblioteca LwIP. A arquitetura foi configurada em topologia mestre-escravo via Ethernet, aproveitando os recursos de *timestamping* por hardware para garantir alta precisão. Os testes práticos validaram a comunicação com sucesso, onde o monitoramento via serial demonstrou o correto cálculo de *offset* e atraso entre as placas.

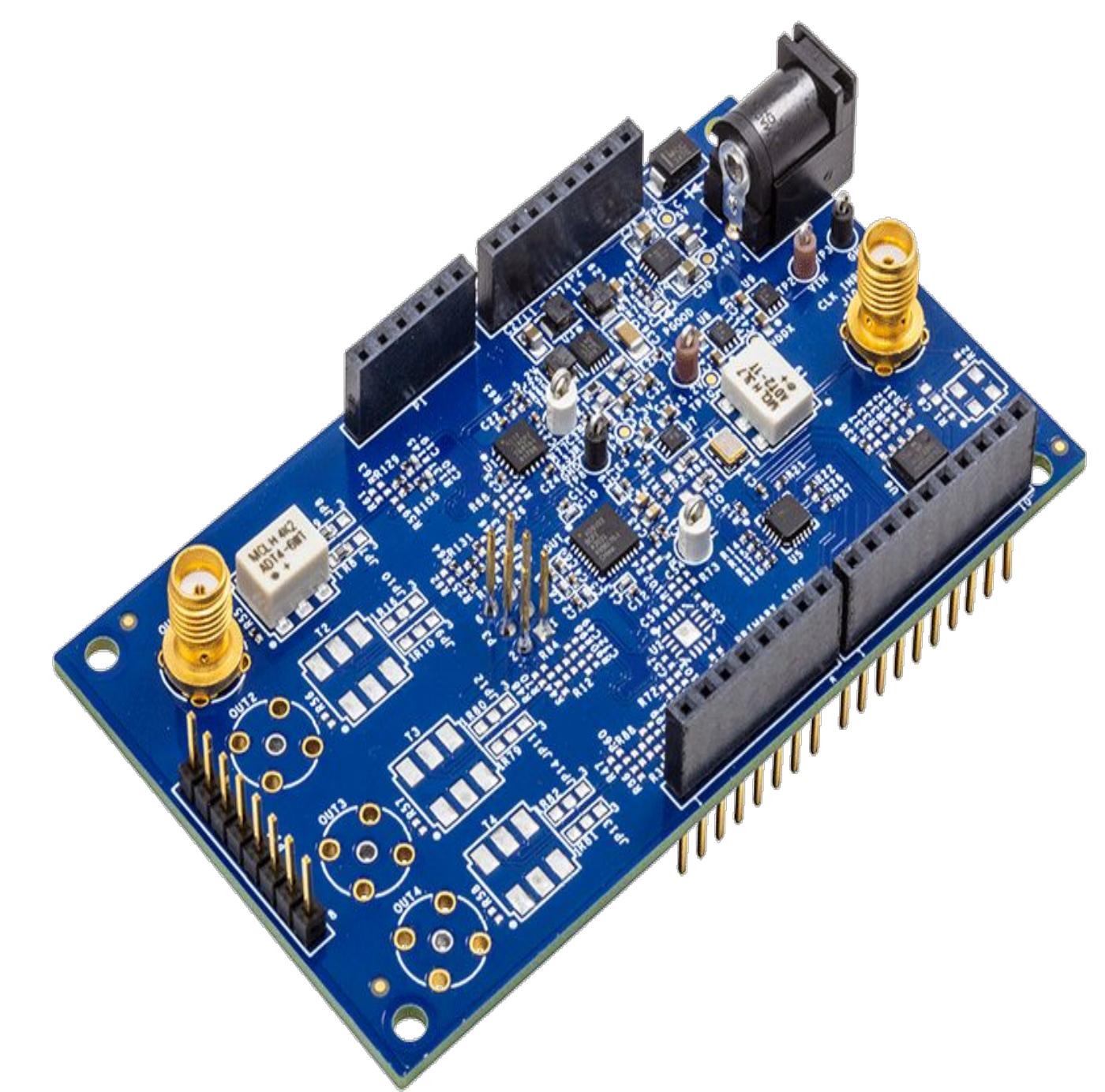

Paralelamente, foi definida a arquitetura do hardware óptico visando a aplicação do método de medição "Picos e Vales". Para a placa moduladora, estabeleceu-se o uso de um conjunto formado por FPGA, microcontrolador (>180MHz) e DAC de alta precisão

**Integrantes:** Ian Aguila Sanchez

Lucas Vianna de Mattos

Weslley de Oliveira e Silva

**Professor(a) Orientador(a):** Prof. Dr. Carlos Eduardo Cugnasca

**Co-orientador(a):** Prof. Dr. Eduardo Lorenzetti Pellini

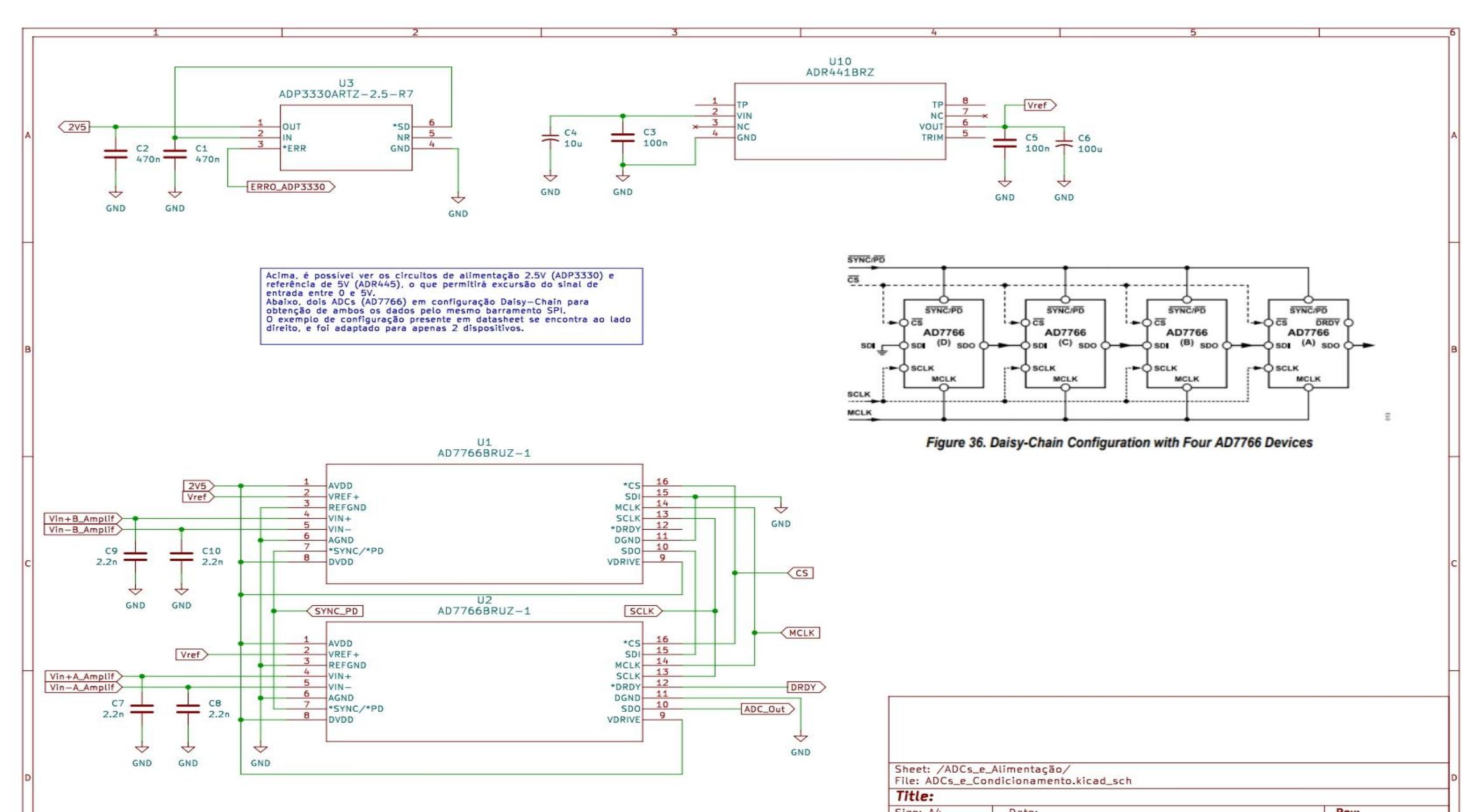

(LVDS), objetivando a síntese precisa da onda senoidal e o controle do laser. Já para a unidade demoduladora, o projeto prevê a utilização de um microcontrolador sincronizado e conversão AD para a captura e processamento da potência luminosa do fotodetector.

Figura 1: Placas utilizando o protocolo PTP

Figura 2: Circuito integrado AD9102BCPZ

## RESULTADOS

Figura 3: Erro entre os pulsos mestre e servo se comunicando via PTP

Figura 4: Parte do esquemático das placas moduladora e demoduladora